# Class-AB Large-Swing CMOS Buffer Amplifier with Controlled Bias Current

Joongsik Kih, Student Member, IEEE, Byungsoo Chang, Deog-Kyoon Jeong, Member, IEEE, and Wonchan Kim, Member, IEEE

Abstract—A class-AB large swing CMOS buffer amplifier with new error amplifier circuits is presented. The error amplifier accurately controls the quiescent current through the output transistors, thereby reducing the variation of the quiescent power dissipation due to process and temperature variations. The buffer amplifier fabricated using 1.2- $\mu m$  CMOS technology occupies an area of 103 mil $^2$  and dissipates an average of 4.7 mW under the quiescent condition with the standard deviation of only 3.2% of the average value. It has -63.6 dB THD with 3.5  $V_{\rm pp}$  output swing into a 300  $\Omega/150$  pF load at 5 kHz.

#### I. INTRODUCTION

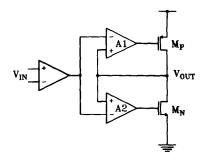

LTHOUGH a class-AB configuration employing a com-A plementary source follower is well suited for minimizing the quiescent power dissipation of the CMOS output buffer amplifier, it has limited applications because of the reduced output swing. Thus an output buffer employing a pseudosource follower shown in Fig. 1 has been widely used for a large swing output [1]-[5]. It is composed of a pair of common source MOS transistors and a pair of complementary error amplifiers. However, the quiescent current of the output buffer shown in Fig. 1 may have a large variation from the design target value due to the random offset voltage of the error amplifier. To reduce such variation an additional block may be inserted, which senses the current flow through the output transistors and controls the current to the target value [2]; or a source follower may be added to the circuit [3]-[5]. Although these approaches could alleviate such problems, the circuit area of the buffer is increased and the additional part of the circuit draws more current. In this paper a large-swing CMOS buffer amplifier using a low-gain, bias-controlled amplifier as the error amplifier is presented. Minimizing the variation of the quiescent current is our primary design goal as well as achieving high performance. This amplifier is designed to drive public telephone lines at voice band frequencies for telecommunication and audio applications.

# II. CIRCUIT DESCRIPTION

The proposed buffer amplifier consists of a high-gain input stage and a unity gain class-AB output stage. The input stage is a conventional two-stage amplifier which is comprised of a differential amplifier and a common source amplifier. The

Manuscript received December 29, 1992; revised June 30, 1993. The authors are with the Department of Electronics Engineering, Seoul National University, Shinlim-Dong, Kwanak-Gu, Seoul, 151-742, Korea. IEEE Log Number 9212082.

Fig. 1. Complementary class-AB output buffer amplifier.

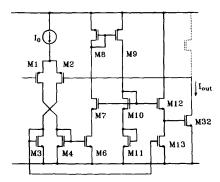

Fig. 2. Circuit schematic of the error amplifier.

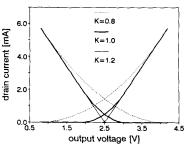

Fig. 3. Simulated drain current of the n-channel and p-channel output transistors with different K values.

output stage includes two complementary error amplifiers and two output transistors as shown in Fig. 1.

Fig. 2 shows the circuit schematic of the error amplifier for driving the n-channel output transistor M32. To enable this error amplifier to be operated with input voltages near the

0018-9200/93\$03.00 © 1993 IEEE

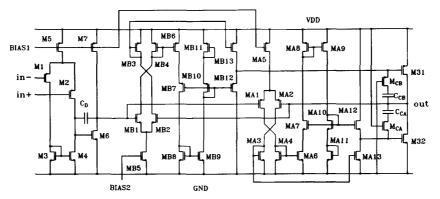

Fig. 4. Complete circuit schematic of the CMOS buffer amplifier.

Fig. 5. Photomicrograph of the buffer amplifier.

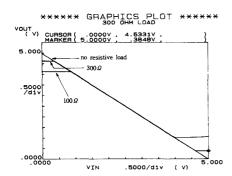

Fig. 6. DC transfer characteristics of the amplifier connected in an inverting unity-gain configuration with 100  $\Omega$ , 300  $\Omega$ , and no resistive load.

negative supply, a source-coupled pair of pMOS transistors are employed. Due to the back-bias effect this pair provides a common-mode input range exceeding the negative supply. The dual of this circuit is used to drive the p-channel output transistor.

To reduce the variation of the quiescent current due to random offset voltage, the open loop gain of the error amplifier must have a relatively small value of an order of 10 [1]. Such low voltage gain can be achieved using a low resistance load like the diode-connected transistor M10. With this configuration we obtained an open loop voltage gain of about 11, so that 2 mV of input offset voltage of the error amplifier results in 22 mV of output offset voltage. At  $I_{\rm D32}=500\,\mu\rm A$ , this amount of output voltage change in the error amplifier causes the output quiescent current to change by about 16%, which is acceptable.

One requirement of the error amplifier is that it has to provide a large voltage swing on the gate of the output transistor to drive the resistive load with a moderately sized output transistor. The maximum voltage swing of a standard differential stage with a current mirror load is only approximately 1.5 V [5]. The proposed error amplifier shown in Fig. 2 can drive the gate of the output transistor M32 up to  $V_{DD}-V_{\rm T,M12}$ . The SPICE simulation shows that the maximum gate voltage swing is 3.2 V, which is about twice the value achieved with the standard configuration.

Another requirement in designing the error amplifier is that it must provide the correct quiescent dc output voltage to yield the desired quiescent current of the output transistor. In the balanced quiescent condition, the drain currents of transistor M1 and M2 are equal to half the bias current  $I_0$ . Because the sizes of transistor M10 and M11 are the same as those of transistor M12 and M13, respectively and the drain currents of these four transistors are the same, the drain voltage of transistor M13 is same as the gate voltage. Thus the drain current of the output transistor M32, the quiescent current, is given by

$$I_{\text{OUT}} = I_{\text{D13}} \cdot \frac{(W/L)_{32}}{(W/L)_{13}}.$$

(1)

The drain current  $I_{D13}$  of M13 is

$$I_{\rm D13} = I_{\rm D3} \cdot \frac{(W/L)_{13}}{(W/L)_3}.$$

(2)

Since the drain current of M3 is equal to half of the bias current  $I_0$ , we can derive the output current by combining (1) and (2), which is given by

$$I_{\text{OUT}} = \frac{1}{2} \cdot \frac{(W/L)_{32}}{(W/L)_3} \cdot I_0.$$

(3)

(3) shows that the quiescent current of this output buffer is linearly related to the bias current  $I_0$  and the W/L ratio of the two transistors M3 and M32.

If we want to decrease the quiescent current without sacrificing the current drive capability, we can make the size of M13 larger. If we increase the size of M13 by a factor of K,

Fig. 7. Transient responses of the amplifier connected in a noninverting unity-gain configuration with 5-V single supply and 300  $\Omega/150$  pF load; (a) a 3.5  $V_{\rm pp}$  step, (b) a 20 mV $_{\rm pp}$  step.

the gate over-drive of M32,  $V_{\rm GS,\,M32}-V_{\rm T,\,M32}$ , is given by

$$\begin{split} &V_{\text{GS, M32}} - V_{\text{T, M32}} \\ &= V_{\text{GS, M10}} + V_{\text{GS, M11}} - V_{\text{GS, M12}} - V_{\text{T, M32}} \\ &= \sqrt{\frac{2\left(\frac{W_{11}}{W_3}\right) \cdot \left(\frac{I_0}{2}\right)}{\mu C_{ox}\left(\frac{W_{10}}{L_{10}}\right)} \left(1 - \sqrt{K}\right) + \sqrt{\frac{2\left(\frac{W_{11}}{W_3}\right) \cdot \left(\frac{I_0}{2}\right)}{\mu C_{ox}\left(\frac{W_{11}}{L_{11}}\right)} \\ &+ \left(V_{\text{T, M10}} - V_{\text{T, M12}}\right) \end{split} \tag{4}$$

assuming  $W_{12}=W_{10},\,W_4=W_3,\,W_6=W_{11},\,{\rm and}\,\,L_{12}=L_{10}.$

(3) can be derived from (4) as a special case of K=1. Since the back-bias effects are almost compensated by taking the difference of the threshold voltages of the transistors M10 and M12 as shown in the last part of (4), the output is a primary function of only  $(W/L)_{32}$ ,  $(W/L)_{13}$ , and  $I_0$ . Fig. 3 shows the simulated drain current of the n-channel and p-channel output transistors at three different K values, 0.8, 1.0, and 1.2. We can see that the quiescent current, the current at 2.5 V, is decreased as K is increased. Because the W/L ratios of the transistor M10 and M12 are small and that of the output transistor M32 is large, a small change of the current of the transistor M10 and M12 causes large change of the output current as shown in Fig. 3.

Fig. 4 shows the complete circuit diagram of the output buffer amplifier. The W/L values of the transistors used in this circuit are summarized in Table I.

TABLE I DEVICE SIZES

| <b>M</b> 1       | 50/5    | MA1               | 100/4 | MB1             | 60/6  |

|------------------|---------|-------------------|-------|-----------------|-------|

| M2               | 50/5    | MA2               | 100/4 | MB2             | 60/6  |

| M3               | 4/6     | MA3               | 30/6  | MB3             | 50/4  |

| M4               | 4/6     | MA4               | 30/6  | MB4             | 50/4  |

| M5               | 12.5/5  | MA5               | 50/5  | MB5             | 50/5  |

| M6               | 16/6    | MA6               | 120/6 | MB6             | 200/4 |

| M7               | 25/5    | MA7               | 6/15  | MB7             | 5/5   |

| M31              | 750/2   | MA8               | 50/5  | MB8             | 50/6  |

| M32              | 500/2.5 | MA9               | 50/5  | MB9             | 50/6  |

| $C_{\mathrm{D}}$ | 15 pF   | MA10              | 6/15  | MB10            | 5/5   |

| $C_{CA}$         | 6 pF    | MA11              | 120/6 | MB11            | 200/4 |

| $C_{CB}$         | 6 pF    | MA12              | 6/15  | MB12            | 5/5   |

|                  |         | MA13              | 120/6 | MB13            | 200/4 |

|                  |         | $M_{\mathrm{CA}}$ | 6.8/3 | M <sub>CB</sub> | 10/2  |

TABLE II OUTPUT BUFFER AMPLIFIER PERFORMANCE SUMMARY ( $V_{DD}$  = 5 V,  $R_L$  = 300  $\Omega$ ,  $C_L$  = 150 pF)

| Parameters                                                   | Measured Results     |  |  |

|--------------------------------------------------------------|----------------------|--|--|

| Die area                                                     | 103 mil <sup>2</sup> |  |  |

| $A_{ m vol}$                                                 | 85 dB                |  |  |

| $F_u$                                                        | 397 kHz              |  |  |

| Phase margin                                                 | 55°                  |  |  |

| PSRR + (dc)                                                  | 101 dB               |  |  |

| (1 kHz)                                                      | 96 dB                |  |  |

| PSRR - (dc)                                                  | 106 dB               |  |  |

| (1 kHz)                                                      | 79 dB                |  |  |

| CMRR (dc)                                                    | 111 dB               |  |  |

| (1 kHz)                                                      | 75 dB                |  |  |

| Harmonic distortion                                          |                      |  |  |

| (freq. = 5 kHz)                                              |                      |  |  |

| $V_{\text{out,pp}} = 3.5 \text{ V}$                          |                      |  |  |

| $R_L = 300 \Omega \text{ HD2}$                               | -71.7 dB             |  |  |

| HD3                                                          | -68.5 dB             |  |  |

| $R_L = 3k\Omega \text{ HD2}$                                 | -66.7 dB             |  |  |

| HD3                                                          | -81.5 dB             |  |  |

| $V_{\text{out,pp}} = 4.0 \text{ V}$                          |                      |  |  |

| $R_L = 300 \Omega \text{ HD2}$                               | -68.5 dB             |  |  |

| HD3                                                          | -66.2 dB             |  |  |

| $R_L = 3 \mathrm{k}\Omega \mathrm{HD2}$                      | -66.0 dB             |  |  |

| HD3                                                          | -82.6 dB             |  |  |

| S/(THD + N)                                                  |                      |  |  |

| $(V_{\text{out,pp}} = 3.5 \text{ V, freq.} = 5 \text{ kHz})$ |                      |  |  |

| $R_L = 300 \Omega$                                           | 63.6 dB              |  |  |

| $R_L = 3 \mathrm{k}\Omega$                                   | 66.4 dB              |  |  |

| Slew rate                                                    | 0.65 V/μs            |  |  |

| $V_{ m offset}$                                              |                      |  |  |

| avg                                                          | -1.3 mV              |  |  |

| std                                                          | 1.5 mV               |  |  |

| Power dissipation                                            |                      |  |  |

| avg                                                          | 4.7 mW               |  |  |

| std                                                          | 0.15 mW              |  |  |

| Output swing                                                 | 4.25 V               |  |  |

AC stability of the complete amplifier is guaranteed when we provide a wide-band output stage and compensate the input stage to produce a dominant pole. The dominant pole in the input stage is formed by the Miller capacitor,  $C_D$ . The compensation of each error amplifier in the output stage is done with a Miller capacitor,  $C_C$  and a zero nulling resistor,  $M_C$ .

## III. EXPERIMENTAL RESULTS

The output buffer amplifier presented was fabricated using 1.2- $\mu$ m, n-well, double-polysilicon, double-metal CMOS technology. A photomicrograph of the output buffer is shown in Fig. 5. The total die area of the amplifier is only 103 mil<sup>2</sup>. The curves in Fig. 6 show the dc transfer characteristics in an inverting unity-gain configuration with different resistive loads under a single 5-V supply. The output voltage swing of the buffer amplifier is 4.25 V and within 0.38 V from each power rail in case of 300  $\Omega$  load. Fig. 7 shows the step response of the buffer amplifier connected in a non-inverting unitygain configuration. Fig. 7(a) and (b) show the large signal response with a 3.5  $V_{\rm pp}$  output and the small signal response with a 20  $\ensuremath{\text{mV}_{\text{pp}}}$  output, respectively. The average value of the measured offset voltage of the amplifier is 1.3 mV and the standard deviation is 1.5 mV. The average power dissipation measured from samples in two different lots is 4.7 mW and the standard deviation is 0.15 mW, which is only 3.2% of the average value. The total harmonic distortion of the amplifier is -63.6 dB with a 3.5  $V_{pp}$  output swing into a 300  $\Omega/150$ pF load at 5 kHz. All the measured results are summarized in the Table II.

# IV. SUMMARY

A full CMOS class-AB buffer amplifier has been presented which has a large output voltage swing on a low impedance load. The amplifier dissipates 4.7 mW of quiescent power to a 300- $\Omega$  load under a 5.0-V single supply and the standard deviation of the quiescent power dissipation is only 3.2% of the average value.

### ACKNOWLEDGMENT

The authors would like to thank Dr. T. G. Kim, J. S. Lee, and J. B. Paek of Hyundai Electronics Industries Co., Ltd. for their support in device fabrication and Dr. K. H. Oh for his encouragement.

### REFERENCES

- [1] B. K. Ahuja, P. R. Gray, W. M. Baxter, and G. T. Uehara, "A programmable CMOS dual channel interface processor for telecommunications applications," IEEE J. Solid-State Circ., vol. SC-19, pp. 892-899, Dec. 1984

- [2] K. E. Brehmer and J. B. Wieser, "Large swing CMOS power amplifier,"

- IEEE J. Solid-State Circ., vol. SC-18, pp. 624–629, Dec. 1983.

[3] J. A. Fisher, "A high-performance CMOS power amplifier," IEEE J. Solid-State Circ., vol. SC-20, pp. 1200–1205, Dec. 1985.

[4] K. Nagaraj, "Large-swing CMOS buffer amplifier," IEEE J. Solid-State

- Circ., vol. SC-24, pp. 181-183, Feb. 1989.

- [5] F. Mistlberger and R. Koch, "Class-AB High-swing CMOS power amplifier," IEEE J. Solid-State Circ., vol. SC-27, pp. 1089-1092, July

Joongsik Kih (S'90) was born in Taegu, Korea in 1958. He received the B.S. and M.S. degrees in electronics engineering Seoul National University, Seoul, Korea, in 1981 and 1983, respectively. At present he is working towards the Ph.D. degree in electronics engineering at Seoul National Univer-

Since 1983 he has been with Hyundai Electronics Industries Co., Ltd., Ichun, Korea, where he worked as a product engineer for the various memories including 16K SRAM, 64K SRAM, 64K DRAM,

256K DRAM, and 1M DRAM. His research interest includes high speed circuits, VLSI system design for the mixed mode signal processing, and a high density DRAM cell.

Byungsoo Chang was born in Kyungbuk in 1957. He received the B.S. degree in electronics engineering from Youngnam University, Taegu, Korea in 1983, and the M.S. degree in electronics engineering from Seoul National University, Seoul, Korea. He has been working toward the Ph.D. degree in electronics engineering at Seoul National University.

In 1985 he joined Korea Telecom and he developed the TDX system family from 1985 to 1990. Since 1991 he has been a manager of the development managing division of networks for

mobile communication and personal communication.

Deog-Kyoon Jeong (S'85-M'89) received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1981 and 1984 respectively, and Ph.D. degree in electrical engineering and computer sciences from the University of California, Berkeley, in 1989.

From 1989 to 1991, he was with Texas Instruments, Dallas, TX, where he was a member of the technical staff working on the modeling and design of BiCMOS gates and the single chip implementation of the SPARC architecture. Since

1991, he has been Assistant Professor of the Department of Electronics Engineering and the Inter-University Semiconductor Research Center, Seoul National University. His main research interests include high speed circuits, VLSI systems design, microprocessor architectures, and memory systems.

Dr. Jeong is a member of ACM.

Wonchan Kim (M'80) was born in Seoul, Korea, on December 11, 1945. He received the B.S. degree in electronics engineering from Seoul National University, Seoul, Korea in 1972. He received the Dip.-Ing and Dr.-Ing degrees in electrical engineering from the Technische Hochschule Aachen, Aachen, Germany, in 1976 and 1981, respectively.

In 1972, he was with Fairchild Semiconductor Korea as a Process Engineer. From 1976 to 1982 he was with the Institut für Theoretishe Electrotecnik, RWTH Aachen.

Since 1982, he has been with the Department of Electronics Engineering, Seoul National University, where he is currently a Professor. His research interests include development of semiconductor devices and design of analog and digital circuits.